## <text><list-item><list-item><list-item><list-item><list-item>

University of Florida, EEL 4744 – File 10 © Drs. Schwartz & Arroyo

## Resets & Interrupts

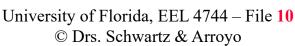

| EEL 4744C JP Apps                                                    | <u>Vec Addr</u><br>FFD6, D7<br>FFD8, D9<br>FFDA, DB<br>FFDC, DD | Interrupt Source<br>Serial Comm. Interface (SCI)<br>Serial Peripheral Interface (SPI)<br>Pulse Accumulator Input Edge<br>Pulse Accumulator Overflow |

|----------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| GCPU++                                                               | FFDE, DF<br>FFE0, E1<br>FFE2, E3<br>FFE4, E5                    | Timer Overflow<br>Timer Output Compare 5<br>Timer Output Compare 4<br>Timer Output Compare 3                                                        |

| Interrupt<br>and Reset                                               | FFE6, E7<br>FFE8, E9<br>FFEA, EA<br>FFEC, ED                    | Timer Output Compare 2<br>Timer Output Compare 1<br>Timer Input Capture 3<br>Timer Input Capture 2                                                  |

| Vectors                                                              | FFEE, EF<br>FFF0, F1<br>FFF2, F3<br>FFF4, F5                    | Timer Input Capture 1<br>Real Time Interrupt<br>IRQ<br>XIRQ                                                                                         |

| University of Florida, EEL 4744 – File 10<br>© Drs. Schwatz & Arrowo | FFF6, F7<br>FFF8, F9<br>FFFA, FB<br>FFFC, FD<br>FFFE, FF        | Software Interrupt (SWI)<br>Illegal Opcode<br>Computer Operating Properly (COP)<br>Clock Monitor<br>RESET 11                                        |

|                                           |            | Pseudo Vector                  | Interrupt Source                                   |

|-------------------------------------------|------------|--------------------------------|----------------------------------------------------|

| <b>EEL 4744</b>                           |            | \$00C4-\$00C6                  | Serial Comm. Interface (SCI)                       |

|                                           |            | \$00C7-\$00C9                  | Serial Peripheral Interface (SPI)                  |

| EEL 4744C: μP Apps                        |            | \$00CA-\$00CC                  | Pulse Accumulator Input Edge                       |

|                                           |            | \$00CD-\$00CF                  | Pulse Accumulator Overflow                         |

| GCPU++ EVE                                | TT         | \$00DO-\$00D2                  | Timer Overflow                                     |

| GCIUTTEVL                                 |            | \$00D3-\$00D5                  | Timer Output Compare 5                             |

| Interrupt Pseud                           |            | \$00D6-\$00D8                  | Timer Output Compare 4                             |

| merrupti i seud                           | 10-        | \$00D9-\$00DB                  | Timer Output Compare 3                             |

| Vectors (with                             | •          | \$00DC-\$00DE                  |                                                    |

|                                           | 1          | \$00DF-\$00E1                  | Timer Output Compare 1                             |

| BUFFALO)                                  |            | \$00E2-\$00E4                  | Timer Input Capture 3                              |

| Dominicoj                                 |            | \$00E5-\$00E7                  | Timer Input Capture 2                              |

|                                           |            | \$00E8-\$00EA                  | Timer Input Capture 1                              |

| <b>BUFFALO</b> memory dump:               |            | \$00EB-\$00ED                  | Real Time Interrupt                                |

| FFD6:00 C4                                |            | \$00EE-\$00F0                  | IRQ                                                |

| FFD8:00 C7 00 CA 00 CE                    | 00 D0      | \$00F1-\$00F3                  | XIRQ                                               |

| FFE0: 00 D3 00 D6 00 D9                   |            | \$00F4-\$00F6                  | Software Interrupt (SWI)                           |

| FFE8: 00 DF 00 E2 00 E5                   | 00 20      | \$00F7-\$00F9<br>\$00FA-\$00FC | Illegal Opcode                                     |

|                                           |            | \$00FD-\$00FF                  | Computer Operating Properly (COP)<br>Clock Monitor |

| FFF0:00 EB 00 EE 00 F1                    |            |                                |                                                    |

| FFF8:00 F7 00 FA 00 FE                    | В6 00      | <u>Vector Addr</u>             | Interrupt Source                                   |

|                                           | $\uparrow$ | FFD6, D7                       | Serial Comm. Interface (SCI)                       |

|                                           | Reset      | FFE0, E1                       | Timer Output Compare 5                             |

|                                           | Pseudo     | FFF0, F1                       | Real Time Interrupt                                |

| University of Florida, EEL 4744 - File 10 |            | FFF2, F3                       | IRQ                                                |

| © Drs. Schwartz & Arroyo                  | Vector     | FFFE, FF                       | RESET 12                                           |

University of Florida, EEL 4744 – File 10 © Drs. Schwartz & Arroyo

University of Florida, EEL 4744 – File 10 © Drs. Schwartz & Arroyo

| EEL 4744С: и Р Арря<br>EEL 4744С: и Р Арря<br>doc 8331:<br>Figure 12-2 | XMEGA: Interrupt<br>execution of Instruction |

|------------------------------------------------------------------------|----------------------------------------------|

| clk                                                                    |                                              |

| Program Counter                                                        |                                              |

| "Instruction"                                                          | inst X "store PC" X JMP                      |

| int req                                                                |                                              |

| int ack                                                                |                                              |

| University of Florida, EEL 4744 – File 10<br>© Drs. Schwartz & Arroyo  | 23                                           |

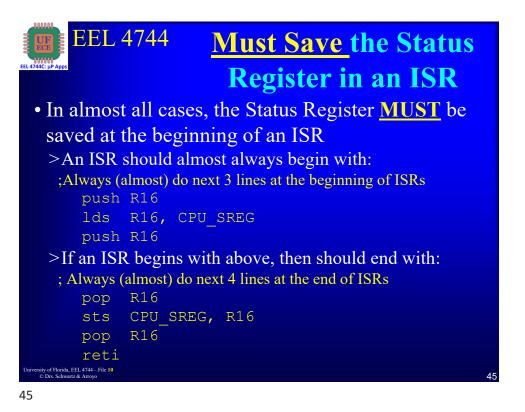

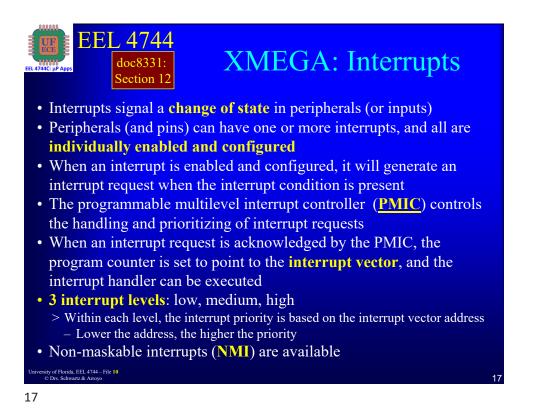

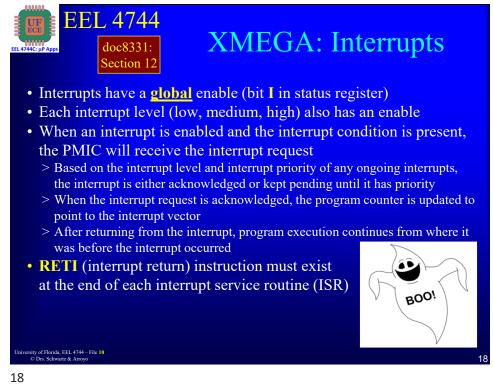

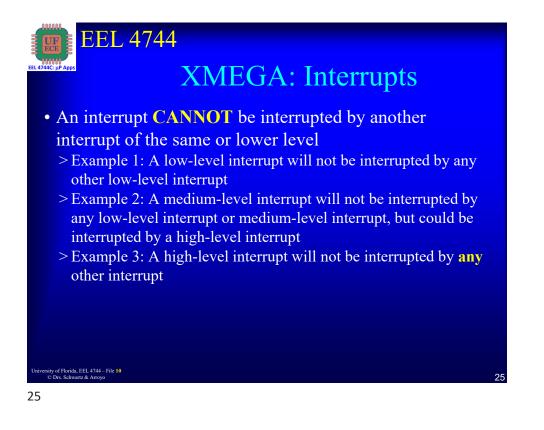

## Section 12 EL 4744 MEGA: Interrupts The PMIC status register contains state information to ensure that the PMIC returns to the correct interrupt level after an RETI Returning from an interrupt will return the PMIC to the state it had before entering the interrupt The status register (SREG) is NOT saved automatically upon an interrupt request (unlike most other processors)

• The RET (subroutine return) instruction can<u>not</u> be used when returning from the interrupt handler routine, as this will **not** return the PMIC to its correct state

University of Florida, EEL 4744 – File 10 24 University of Florida, EEL 4744 – File 10 © Drs. Schwartz & Arroyo

University of Florida, EEL 4744 – File 10 © Drs. Schwartz & Arroyo

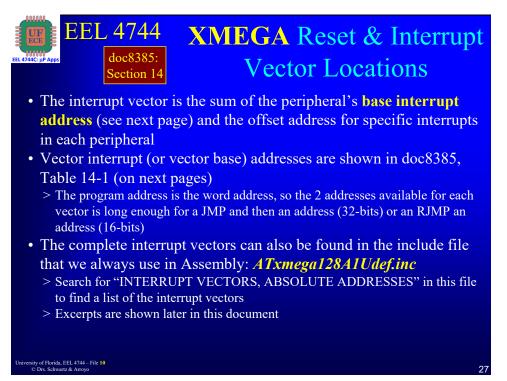

| EEL 4<br>doc833<br>Table 1                                          | <sup>85:</sup> Vector I | A Reset & Interrupt<br>Locations – Part 1/4       |  |  |

|---------------------------------------------------------------------|-------------------------|---------------------------------------------------|--|--|

| Program address<br>(base address)                                   | Source                  | Interrupt description                             |  |  |

| 0x000                                                               | RESET                   |                                                   |  |  |

| 0x002                                                               | OSCF_INT_vect           | Crystal oscillator failure interrupt vector (NMI) |  |  |

| 0x004                                                               | PORTC_INT_base          | Port C interrupt base                             |  |  |

| 0x008                                                               | PORTR_INT_base          | Port R interrupt base                             |  |  |

| 0x00C                                                               | DMA_INT_base            | DMA controller interrupt base                     |  |  |

| 0x014                                                               | RTC_INT_base            | Real time counter interrupt base                  |  |  |

| 0x018                                                               | TWIC_INT_base           | Two-Wire interface on port C interrupt base       |  |  |

| 0x01C                                                               | TCC0_INT_base           | Timer/counter 0 on port C interrupt base          |  |  |

| 0x028                                                               | TCC1_INT_base           | Timer/counter 1 on port C interrupt base          |  |  |

| 0x030                                                               | SPIC_INT_vect           | SPI on port C interrupt vector                    |  |  |

| 0x032                                                               | USARTC0_INT_base        | USART 0 on port C interrupt base                  |  |  |

| 0x038                                                               | USARTC1_INT_base        | USART 1 on port C interrupt base                  |  |  |

| iversity of Florida, EEL 4744 – File 10<br>© Drs. Schwartz & Arroyo |                         |                                                   |  |  |

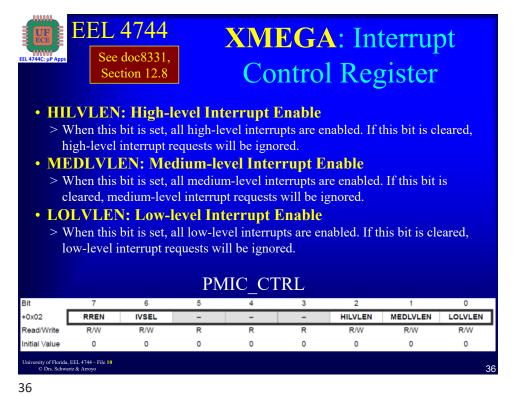

| • IV\$<br>> V<br>s' | SEL: In<br>When the Cart of the | terrupt<br>VSEL bit i<br>application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>Vector</b><br>s cleared<br>s section | Select (no<br>(zero), the<br>in flash. W | o <b>t norm</b><br>e interruj | pt vectors a<br>s bit is set ( | are placed a<br>(one), the in | at the<br>nterrupt |

|---------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------|

| d                   | evice dat                       | asheet for the sheet for the s | ne absolu<br>protectio                  | te address.                              | . This bit<br>sm.             | ction of the<br>t is protecte  |                               | er to the          |

| d                   | evice data<br>onfigurat<br>7    | asheet for the second s | ne absolu<br>protectio                  | te address<br>n mechani                  | . This bit<br>sm.             |                                |                               | 0                  |

| d<br>c              | evice data<br>onfigurat         | 6<br>IvseL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ne absolu<br>protectio<br>PM            | te address<br>n mechani                  | . This bit<br>sm.<br>RL       | t is protecto                  | ed by the                     |                    |

| d<br>c<br>Bit       | evice data<br>onfigurat<br>7    | asheet for the second s | ne absolu<br>protectio<br>PM<br>5       | ite address.<br>n mechani<br>IIC_CT<br>4 | . This bit<br>sm.<br>RL<br>3  | t is protecto                  | ed by the                     | 0                  |

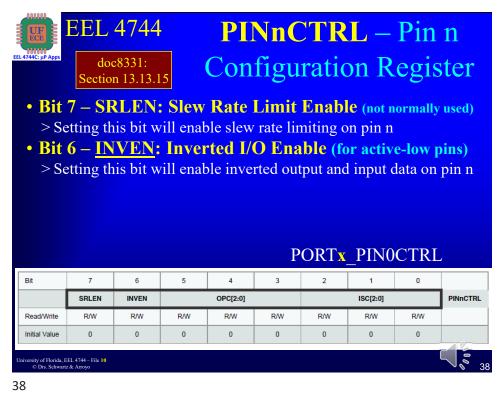

| EEL 4744: ил Арры<br>вес 4744: ил Арры<br>doc8331:<br>Section 13.13.15 |           |                            | – Pin n<br>1 Register      |  |  |

|------------------------------------------------------------------------|-----------|----------------------------|----------------------------|--|--|

| • Bit 5:3 – OPC: Output                                                | OPC[2:0]  | Description<br>Pull config | Description<br>Pull config |  |  |

| and Pull Configuration                                                 | 000       | Totem-pol                  | N/A                        |  |  |

| See doc8331, Table 13-5<br>– Totem, Bus-keeper, pull-                  | 001       | Totem-pol                  | Bus-keeper                 |  |  |

| down, pull-up, wired-                                                  | 010       | Totem-pol                  | Pull-down (on input)       |  |  |

| OR, wired-AND,                                                         | 011       | Totem-pol                  | Pull-up (on input)         |  |  |

|                                                                        | 100       | Wired-OR                   | N/A                        |  |  |

|                                                                        | 101       | Wired-AND                  | N/A                        |  |  |

|                                                                        | 110       | Wired-OR                   | Pull-down                  |  |  |

| PORTx PIN0CTRL                                                         | 111       | Wired-AND                  | Pull-up doc8331:           |  |  |

| Bit 7 6 5                                                              | 4 3 2     | 2 1 0                      | Table 13-5                 |  |  |

| SRLEN INVEN OP                                                         | C[2:0]    | ISC[2:0]                   | PINnCTRL                   |  |  |

| Read/Write R/W R/W R/W                                                 | VW R/W R/ | W R/W R/W                  | /                          |  |  |

| Unive Initial Value 0 0 0                                              | 0 0 0     | 0 0 0                      | 39                         |  |  |

| UCE<br>44744C: μP Apps                      | doo     | <b>4744</b><br>c8331:<br>n 13.13.1 |                    |          |      |         |                | L – ]<br>on Re     |            |                  |

|---------------------------------------------|---------|------------------------------------|--------------------|----------|------|---------|----------------|--------------------|------------|------------------|

| • Bit                                       | 2:0-    | ISC[2                              | :0]:               |          |      | ISC     | C <b>[2:0]</b> | Group<br>Config    | Desc       | ription          |

| Inp                                         | ut/Sei  | nse Co                             | onfigu             | ration   |      | 000     | 0              | BothEdge           | s Botl     | 1 edges          |

| >T                                          | he sens | e config                           | guratior           | 1 decide | s    | 00      | 1              | Rising             | Risi       | ng edge          |

|                                             | -       |                                    | trigger            | 010      | 0    | Falling | Fall           | ing edge           |            |                  |

|                                             | -       | s and ev                           | zents<br>er is dis | ha       | 01   | 1       | Level          | Low                | 7          |                  |

|                                             | -       |                                    | read in            |          | .110 | 10      | 0-110          |                    | Res        | erved            |

|                                             | gister  |                                    | Tx_PI              |          | RL   | 111     | 1              | Input_<br>Disabled | d          | abled<br>oc8331: |

| Bit                                         | 7       | 6                                  | 5                  | 4        | 3    |         | 2              | 1                  | <b>T</b> a | able 13-         |

|                                             | SRLEN   | INVEN                              |                    | OPC[2:0] |      |         |                | ISC[2:0]           |            | PINnCTRL         |

| Read/Write                                  | R/W     | R/W                                | R/W                | R/W      | R/W  | /       | R/W            | R/W                | R/W        |                  |

| Initial Value                               | 0       | 0                                  | 0                  | 0        | 0    |         | 0              | 0                  | 0          |                  |

| Jniversity of Florida, E<br>© Drs. Schwartz |         |                                    |                    |          |      |         |                |                    |            |                  |

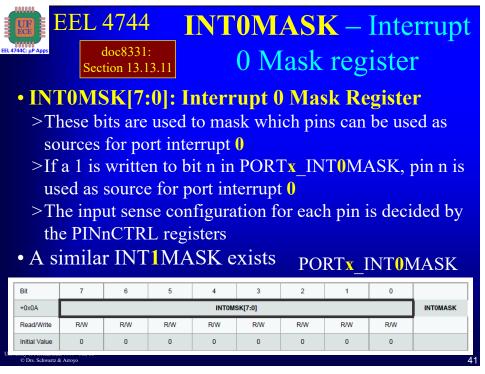

|           | С: µР Арря                                                | EL 47<br>doc <sup>a</sup><br>Section | 8331:          |             |                 |            |                     |                   | ntern<br>,ister | - <b>-</b> |

|-----------|-----------------------------------------------------------|--------------------------------------|----------------|-------------|-----------------|------------|---------------------|-------------------|-----------------|------------|

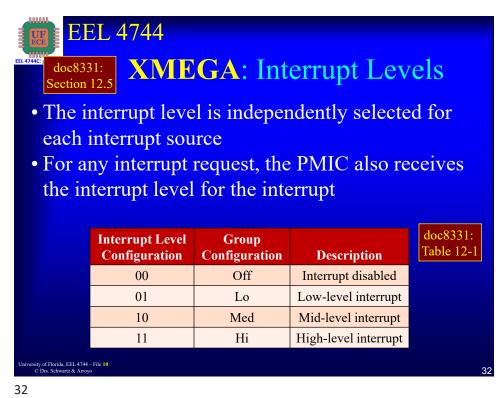

| •         | >The<br>the i                                             | se bits<br>nterru                    | enab<br>pt lev |             | inter<br>lescri | rup<br>bec | ot n (n<br>l in "Iı | = 0 or<br>nterrup |                 |            |

|           | Interru<br>Configu                                        |                                      | Γ              | Descriptio  | on              | do         | c8331:              |                   |                 |            |

|           | 0                                                         | )                                    | Inte           | rrupt disa  | bled            | Tal        | ble 12-1            |                   |                 |            |

|           | 0                                                         | 1                                    | Low            | -level inte | errupt          |            |                     |                   |                 |            |

| -         | 1                                                         | )                                    | Mid            | -level inte | errupt          |            |                     |                   |                 |            |

|           | 1                                                         | 1                                    | High           | -level int  | errupt          |            |                     | PORT              | x_INT           | CTRL       |

| Bit       |                                                           | 7                                    | 6              | 5           | 4               | -          | 3                   | 2                 | 1               | 0          |

| +0x09     |                                                           | -                                    | -              | -           | -               |            | INT1LV              | <u>· ·</u>        | INTOL           |            |

| Read/     |                                                           | R                                    | R<br>0         | R<br>0      | R<br>0          |            | R/W<br>0            | R/W               | R/W             | R/W<br>0   |

| Universit | Value<br>ty of Florida, EEL 4744<br>Drs. Schwartz & Arroy |                                      | U              | U           | U               |            | U                   | U                 | U               | 42         |

University of Florida, EEL 4744 – File 10 © Drs. Schwartz & Arroyo

| EL 4744C: µP Apps                              | Sec                                                                                                                                                                                                                                                                                  | <b>4744</b><br>doc8331<br>tion 13.1 | :<br>3.13 |                      | Flag | gs R | egis   |        | upt      |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------|----------------------|------|------|--------|--------|----------|--|--|

| >Tl<br>th<br>so<br>>W                          | <ul> <li>Bit 1:0 – INTnIF: Interrupt n Flag</li> <li>The INTnIF flag is set when a pin change/state matches the pin's input sense configuration, and the pin is set as source for port interrupt n</li> <li>Writing a one to this flag's bit location will clear the flag</li> </ul> |                                     |           |                      |      |      |        |        |          |  |  |

|                                                |                                                                                                                                                                                                                                                                                      |                                     | POR       | Γ <mark>x_</mark> IN | TFLA | GS   |        |        |          |  |  |

| Bit                                            | 7                                                                                                                                                                                                                                                                                    | 6                                   | 5         | 4                    | 3    | 2    | 1      | 0      |          |  |  |

| +0x0C                                          | -                                                                                                                                                                                                                                                                                    | -                                   | -         | -                    | -    | -    | INT1IF | INTOIF | INTFLAGS |  |  |

| Read/Write                                     | R                                                                                                                                                                                                                                                                                    | R                                   | R         | R                    | R    | R    | R/W    | R/W    |          |  |  |

| Initial Value                                  | 0                                                                                                                                                                                                                                                                                    | 0                                   | 0         | 0                    | 0    | 0    | 0      | 0      |          |  |  |

| University of Florida, EE<br>© Drs. Schwartz & |                                                                                                                                                                                                                                                                                      |                                     |           |                      |      |      |        |        | 43       |  |  |

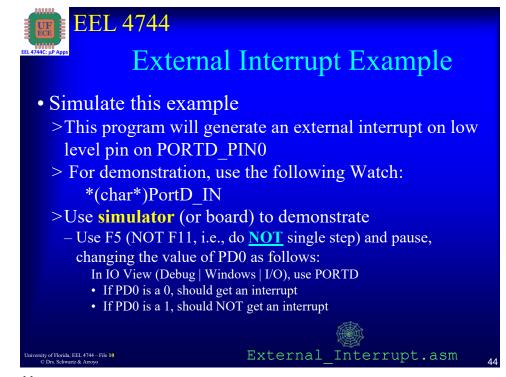

44

University of Florida, EEL 4744 – File **10** © Drs. Schwartz & Arroyo